深入CC3200(4)—GPIO相关函数解析(1)

admin 于 2017-07-27 13:26 发表在 CC3200开发,6164次阅读,暂无评论

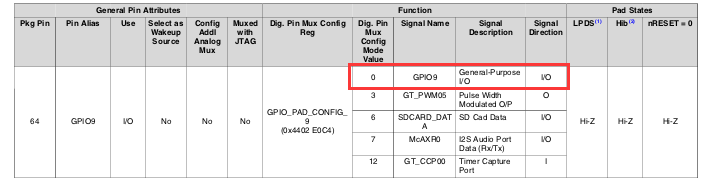

确认各参数的方法:

Verilog写一个简单的UART发送模块 推荐

johncheapon 于 2017-07-23 13:05 发表在 FPGA 开发,4492次阅读,暂无评论

UART差不多是最简单的通信协议,非常适合用来练习FPGA编程。

笔者根据UART协议,尝试按照自己的思路去写一个UART发送功能模块,波特率完全固定,无奇偶校验,数据位为固定的8bit。这算是最简单的通信了,但笔者从构思到RTL实现还是花了约两个小时才完成。

状态机(FSM)在verilogHDL数字逻辑设计中用的很多,但笔者采用了便于理解的计数器的方式,其核心部分无非是一个比特计数器和一个帧计数器,其余的逻辑所做的就是在适当的时刻控制它们增减,非常容易读懂。

这个模块笔者已在FPGA中完成验证,在SecureCRT或MiniCom中能打印"HELLO"

FRAM读写模块设计与仿真-Verilog实现 推荐

johncheapon 于 2017-07-17 16:18 发表在 FPGA 开发,4158次阅读,1条评论

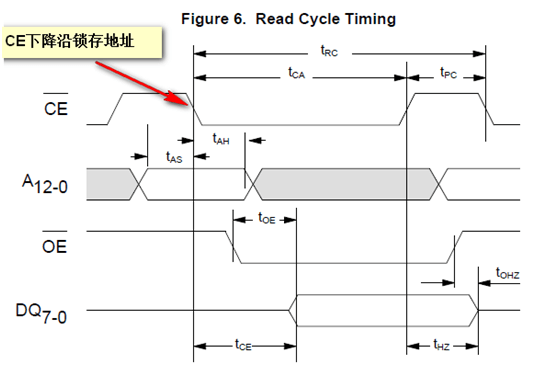

本文以赛普拉斯公司的FM16W08为例,用VerilogHDL语言设计了一个FRAM读写模块,并成功在Modelsim环境中进行了单字节的读写验证。

Win7下搭建Apache+Mysql+PHP开发环境

admin 于 2017-07-16 17:15 发表在 PHP后端服务开发,3928次阅读,暂无评论

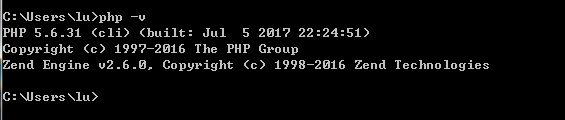

执行 php -v 指令输出:

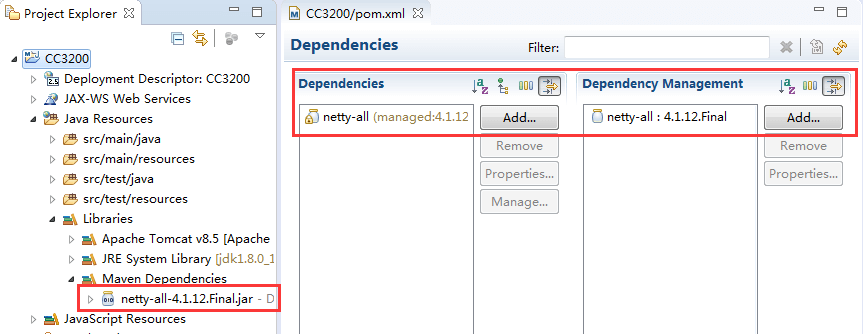

JavaEE开发—(3)Eclispe下Maven添加Netty

admin 于 2017-07-15 16:23 发表在 PHP后端服务开发,4282次阅读,暂无评论

添加 netty 包支持:

JavaEE开发—(2)最新Eclispe下Maven配置

admin 于 2017-07-14 16:15 发表在 PHP后端服务开发,2736次阅读,暂无评论

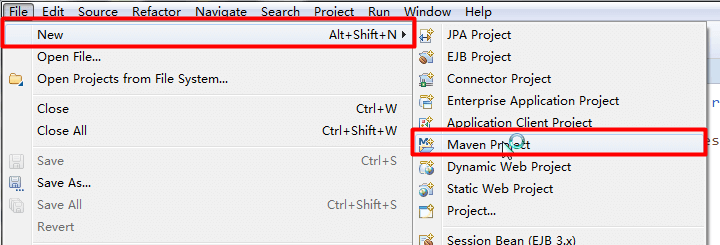

直接创建Maven项目: